半导体存储器没怎么学会,复习一下。

半导体存储器

1. 概述

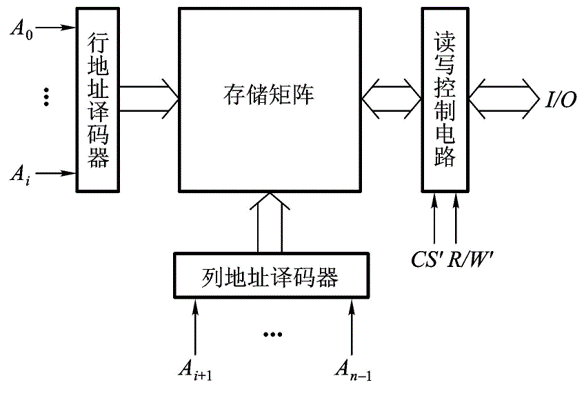

1.1 基本结构

1.2 概念

- RAM:随机存储器

具备读写功能,目前一字节为单位访存。是易失存储器。

- ROM:只读存储器

不具备在线写操作功能,一般需要高电压写,紫外线或高电压擦除,一般装机之前厂家就写好了。是非易失存储器。

- 易失存储器:

下电后数据丢失。

- 非易失存储器:

下电后数据不丢失。

- SRAM:静态随机存取存储器

只要供电存在,存储器的数据就保持。

- DRAM:动态随机存取存储器

存储器需要周期性刷新,否则数据就会丢失。

2. 只读存储器(ROM)

2.1 掩膜只读存储器(Mask ROM)

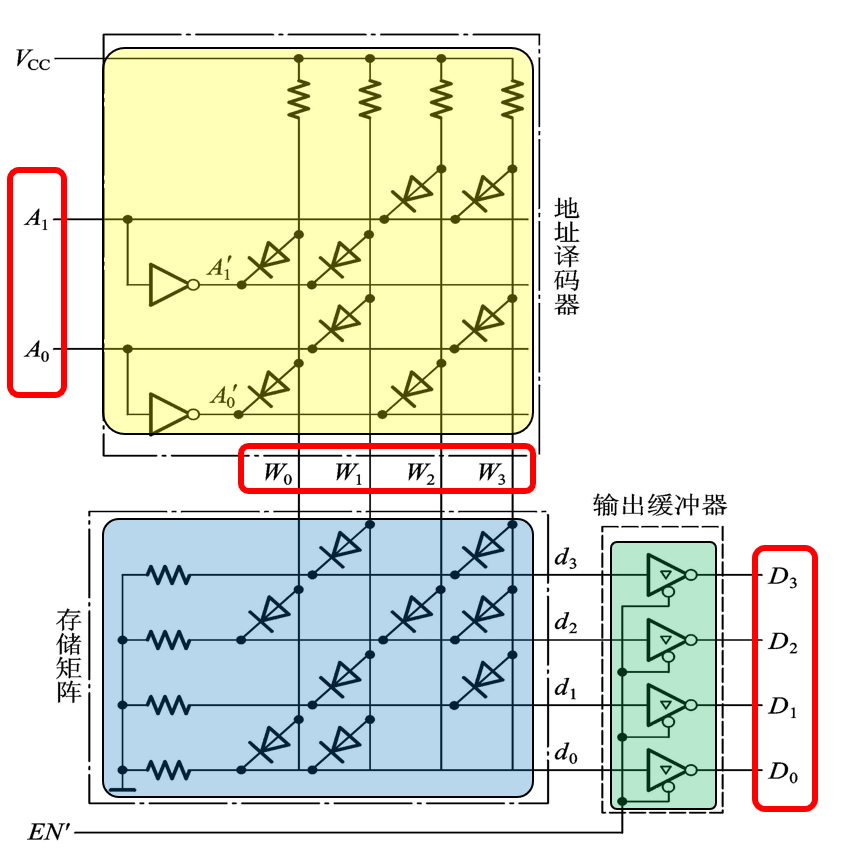

- 基本结构

- 存储矩阵:由众多存储单元(cell)组成,存储单元可以是二极管、双极型三极管或MOS管。

- 地址译码器:地址线为n位,可以译码出$2^n$个地址单元,如果每个单元是M位二进制数,则总容量为$2^n\times M$(bits)。地址编码为$0\sim 2^n-1$。

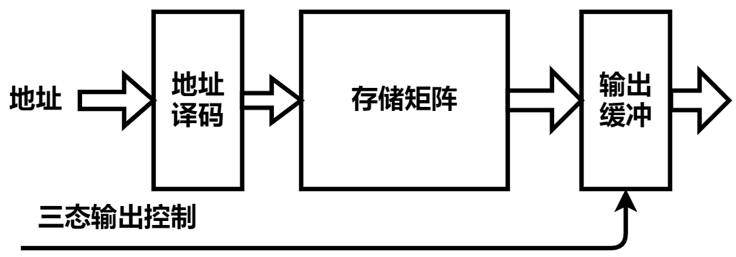

- 输出缓冲器:实现对输出状态的三态控制,以便与总线连接。

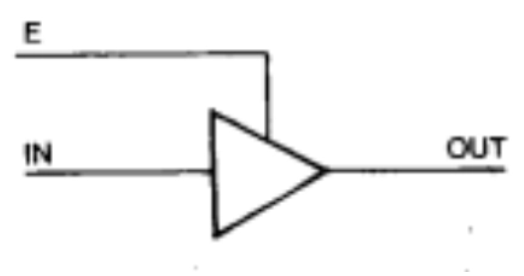

三态控制:如果要在一条信号线上连接多个触发器,而每个触发器可以根据需要与信号线连通或断开,当连通时可以传送“0”或“1”,断开时对信号线上的信息不产生影响,就需要一个特殊的电路加以控制,此电路即为三态输出电路,又称为三态门。

这是一个三态门↑

- 工作原理:

内部结构:

$W_0\sim W_3$为字线,$D_0\sim D_3$为位线,交叉的点就是一个存储单元。

1、地址译码器

就是以前学的译码器。请参见第7讲ppt的45页:二极管阵列构成的译码器。大致考虑思路是:$V_{CC}$的高电平加到二极管的一端(不妨记为A),只要另一端(不妨记为B)是低电平就会导通,把A端拉到低电平(比如硅二极管的导通压降,0.7V),A端又接了输出,因此输出是低电平(注意低电平有效)。

地址译码器会把二线输入的地址($A_0A_1$)译成二进制,这样$W_0,W_1,W_2,W_3$中只有一条线被选到(也就是只有一条线输出为1,其它为0)。

“与”阵列:我们称这个阵列是“与”阵列。什么意思呢?比如上图里$W_0=A_0’A_1’$,这就是逻辑“与”嘛,只有两个条件同时成立$W_0$才能是高电平。

2、存储矩阵

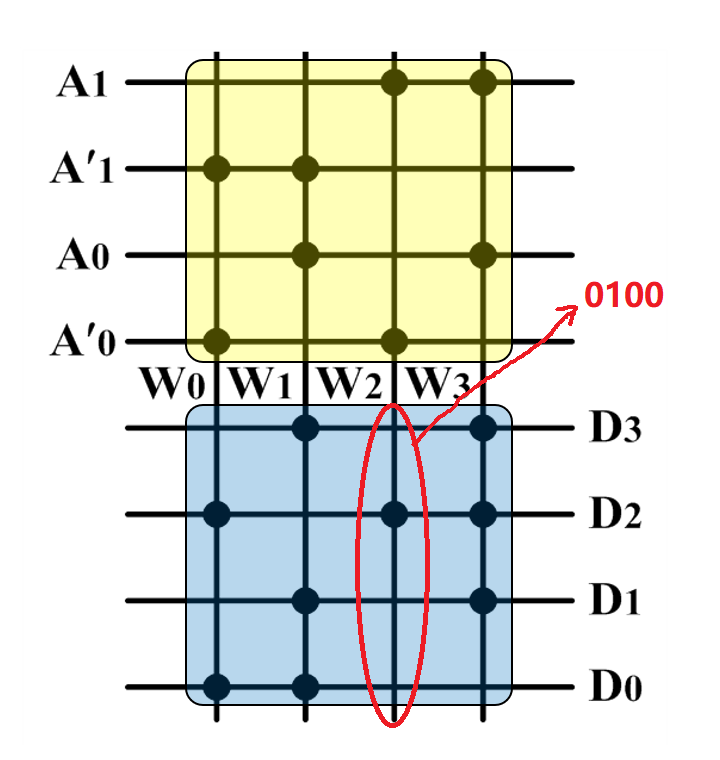

这里面写了信息。我们前面选了一个地址,译码之后连到存储矩阵来,这样存储矩阵里面的一条4位二进制信息就被选中,并反映到$D_3D_2D_1D_0$上。我们来看一个上面内部结构的简化图片(这个很好理解,不解释了):

当$A_1A_0=10$时,$W_2=1$,而其它字线均为低电平。看到点$(W_2,D_2)$有个二极管,这样$W_2$就被接到了$D_2$上,但是没有被接到$D_0,D_1,D_3$上,因此输出的这条二进制信息为$D_3D_2D_1D_0=0100$。(如上图所示)

“或”阵列:我们称这个阵列是“或”阵列。什么意思呢?比如上图里$D_2=W_0+W_1+W_3$,这就是逻辑“或”嘛,只要三个条件里有一个成立$D_2$就是高电平。

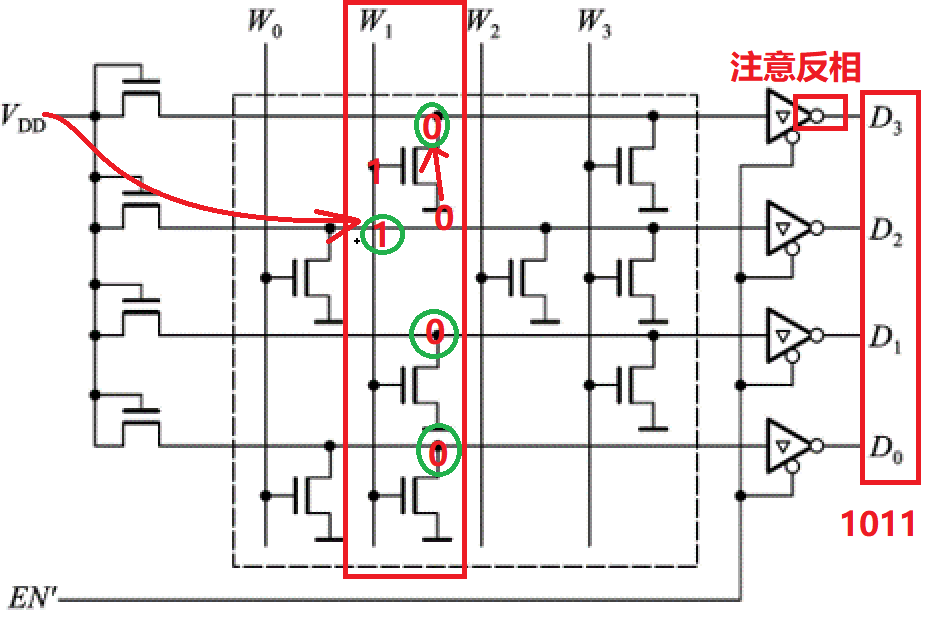

存储矩阵也可以用二极管实现,我把分析过程画下面图里了。

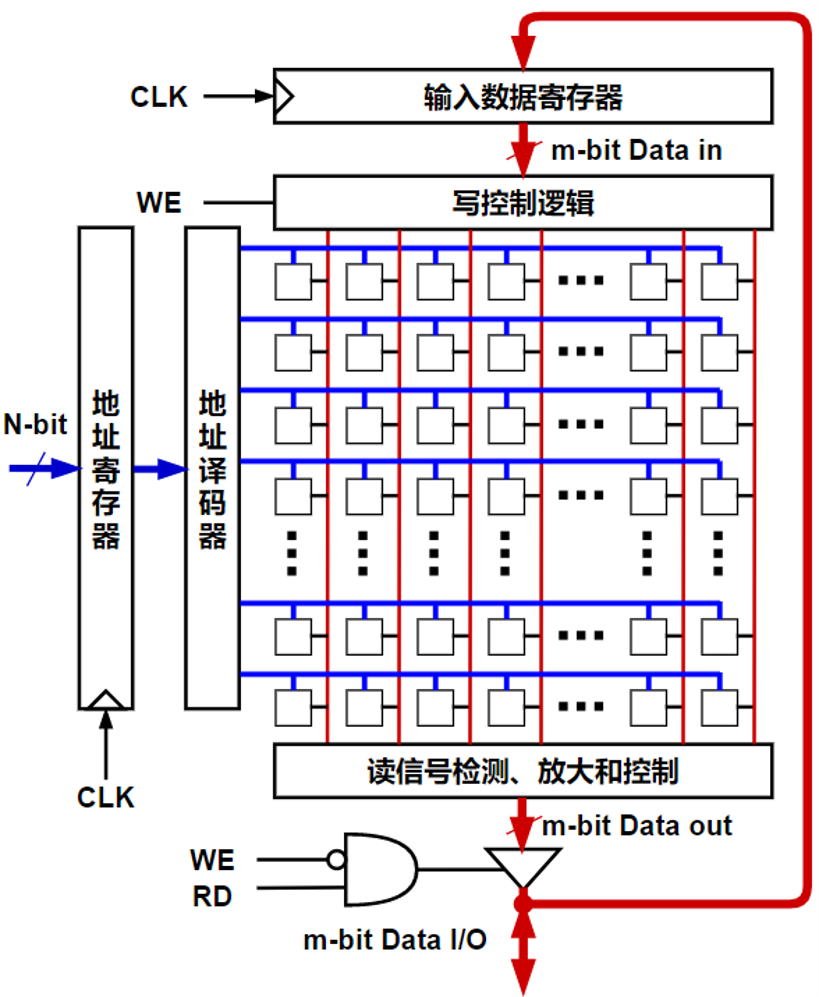

3、输出缓冲

可以提高带负载能力(为啥?)、实现电平变换(比如上图的反相)、实现三态控制以便连接总线(参考上面的三态控制注释)。

2.2 可编程只读存储器(PROM)

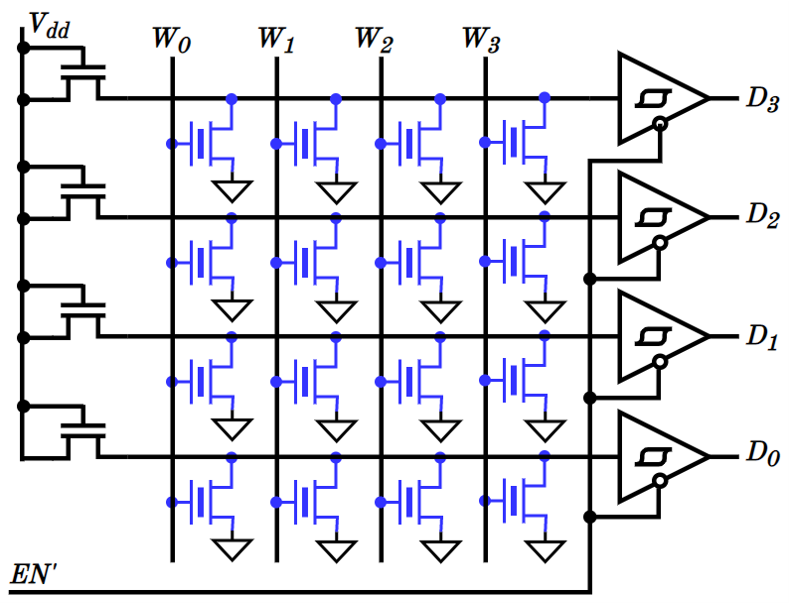

整体结构和掩膜ROM一样,加了一条功能:输入和编程控制。它在存储矩阵的所有交叉点上都制作了存储元件(MOS管),如上图所示。这相当于在所有的存储单元上都存储了“1”。我们想在存储矩阵里写入信息,就是要把一些“1”改成“0”。

下面介绍集中可编程单元实现方法:

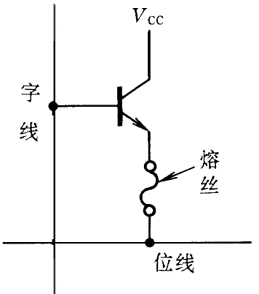

- 熔丝型PROM

想写入“0”时,只要把熔丝熔断即可。但这样就只能编写一次。

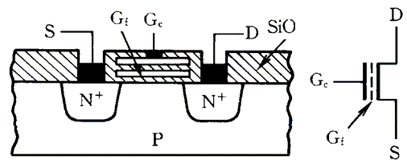

- 用紫外线擦除的可编程ROM(UVEPROM,也可不严谨地称为EPROM)

原理:和普通MOS管相比,除控制栅$G_c$外,还多了一个浮置栅$G_f$。如果浮置栅上充了负电,即使$G_c$加正常的逻辑高电平,衬底的电子也难以被吸上来形成导电沟道,因此这时不会导电,相当于“0”;如果$G_f$未充负电,相当于普通MOS管,$G_c$在正常逻辑高电平下导通。

写入:就是充电。方式是雪崩击穿:源极$S$接低电平,漏极$D$接高电平(6V左右),同时在控制栅上加一个幅度为12V的正脉冲。这时漏极-源极间会发生雪崩击穿,一部分速度高的电子便穿过氧化层到达浮置栅,在浮置栅上形成充电电荷。如下图所示:

擦除:需要紫外线擦除。

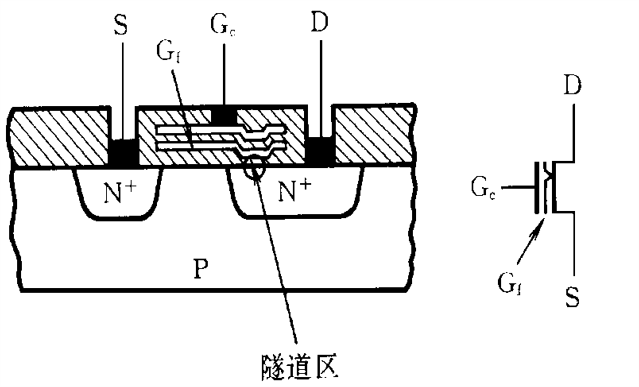

- 用电擦除的可编程ROM(EEPROM)

原理:同上。

写入:隧道效应。隧道区(见上图)的电场强度$>10^7V/cm$时,便在$D$和$G_f$之间形成导电隧道,电子可以双向通过,形成电流。写入的时候,控制栅和源漏极之间有较大的正向压差,电子经由隧道区进入浮置栅,形成充电电荷。如下图所示:

擦除:隧道效应。擦除的时候,控制栅和源漏极之间有较大的负向压差,电子从浮置栅回被拉出,充电电荷消失。如下图所示:

- 可编程只读存储器(Flash Memory,闪存)

原理:同上。只不过浮置栅和衬底氧化层之间的距离小了很多(EPROM中为30-40nm,闪存中是10-15nm)。这样就增大了电容($C=\frac{\epsilon S}{d}$)。因此当控制栅和源极之间加电压时,大部分的压降都落在浮置栅和源极之间($\Delta U=\frac{Q}{C}$)。

写入:雪崩击穿。

擦除:令控制栅$G_c$处于0电平,在源极接入12V正脉冲,这样根据上面的分析,大部分脉冲电压都加在浮置栅和源极之间,从而将浮置栅电子经由隧道释放,实现擦除。

3. 随机存储器

基本结构: